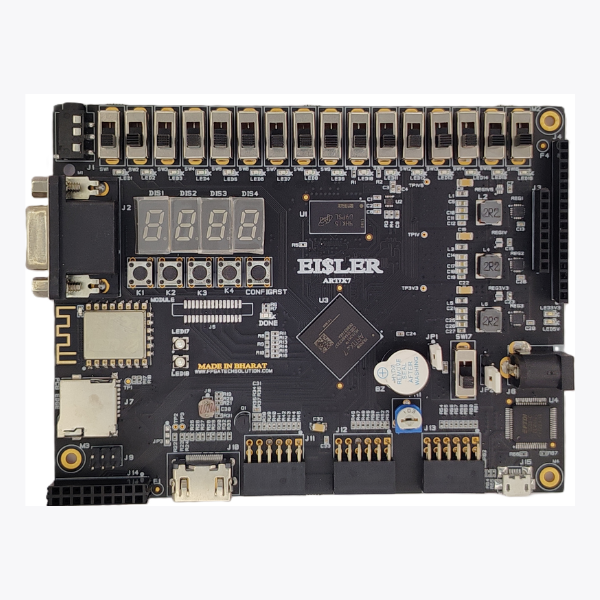

Technical Specification

- Xilinx XC7A35T-1CSG324C ARTIX7, 12,800 logic cells in 5000 slices

- 2Gb ddr3 memory

- 16 user switches

- 16 user LEDs

- 4 user pushbuttons

- 100MHz clock

- 4-digit 7-segment display

- Three Pmod ports (24GPIO), can be used for 12 diff channel xadc

- ESP-12E WiFi

- Buzzer

- RGB LED

- HDMI out

- 12Bit VGA output

- USB-UART

- Serial Flash 32Mbit

- LM35 temperature sensor connected to XADC pin

- LDR connected to XADC pin

- Preset connected to XADC pin

- 8Bit SPI DAC

- SD CARD

- Stereo 3.5mm Jack (Audio out)

- USB-JTAG port for FPGA programming and communication (support Vivado)

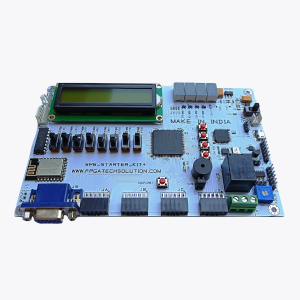

- 16BY2LCD (Add on)

- Rpi mipi csi camera 5MP (Add on)

- OV7670 VGA camera (Add on)

- Matrix keypad 4×4 (Add on)

- TFT display 160×128 (Add on)

- OLED display 128*32 (Add on)

- Relay driver board (Add on)

- Stepper/DC/Servo motor driver (Add on)

- Wooden Box Enclosure (Add on)

Reviews

There are no reviews yet.