Features

The Spartan-7 FPGA is optimized for high performance logic, and offers more capacity, higher performance, and more resources than earlier designs. Spartan-7 XC7S15FTGB196-1 features include:

- 12,800 logic cells in 5000 slices (each slice contains four 6-input LUTs and 8 flip-flops);

- 360 Kbits of fast block RAM;

- Two clock management tiles, each with a phase-locked loop (PLL);

- 20 DSP slices;

- Internal clock speeds exceeding 450MHz;

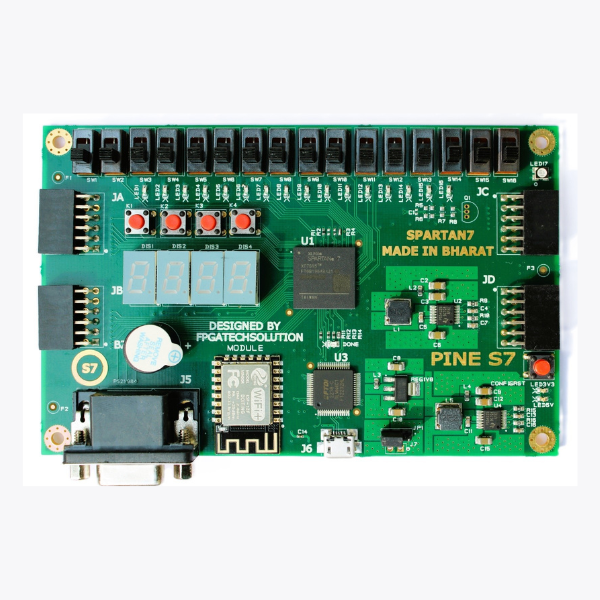

The PINE-S7 also offers an improved collection of ports and peripherals, including:

- 16 user switches

- 16 user LEDs

- 4 user pushbuttons

- 100MHz clock

- 4-digit 7-segment display

- Four Pmod ports (32GPIO)

- ESP-12E WiFi

- Buzzer

- RGB LED

- VGA output

- USB-UART Bridge

- Serial Flash

- USB-JTAG port for FPGA programming and communication (support Vivado )

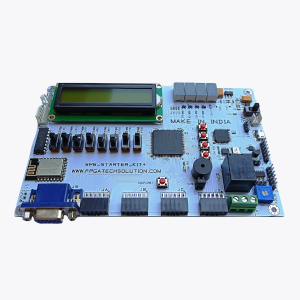

Add on module available:

- 16By2LCD

- 4X4 matrix keypad

- OV7670 Camera module

- 4 user pushbuttons

- 4 channel ADC & DAC

Reviews

There are no reviews yet.